# Fabrication and Characterization of a Low-Cost, Wafer-Scale Radial Microchannel Cooling Plate

M. P. Y. Desmulliez, *Member, IEEE*, A. J. Pang, M. Leonard, R. S. Dhariwal, W. Yu, E. Abraham, Gy. Bognár, A. Poppe, *Member, IEEE*, Gy. Horvath, Zs. Kohari, M. Rencz, *Member, IEEE*, D. R. Emerson, R. W. Barber, O. Slattery, F. Waldron, and N. Cordero

Abstract—The modeling, simulation, fabrication, and testing of a microchannel cooling plate for microelectronic packaging applications are described in this paper. The cooling component uses forced convection of gas injected inside 128 microchannels of 100- $\mu$  m width and 70- $\mu$ m height. The nickel-based plate is fabricated on a glass substrate using a two-layer electroforming process using UV-LIGA technology. The thermal behavior of the microchannel cooling device is investigated by using the measurement of partial thermal resistances through the use of the structure functions method. Heat transfer coefficient values of 300 W/m² K have been measured for a nitrogen flow rate of 120 l/h.

Index Terms—Cooling devices, microchannel, modeling and simulation, thermal management, UV-LIGA.

#### I. INTRODUCTION

THE RAPID advances in transistor density and switching frequency of VLSI circuits as encountered in microprocessors have induced dramatic increases in die heat flux and power consumption at all levels of electronic packaging [1], [2]. Such increases in thermal dissipation have motivated the demand for more efficient cooling mechanisms at the die, component, PCB, and system levels [3]. Of interest in this paper are heat sinks which are low cost, mass produced and can be potentially manufactured and assembled on a wafer

Manuscript received October 08, 2007; revised June 24, 2008. First published November 18, 2008; current version published February 27, 2009. This work was supported in part by the U.K. Engineering and Physical Sciences Research Council (EPSRC) under Project "Microengineered axial-flow pumps and turbines" (GR/N18925) and the 3D-Mintegration Grand Challenge project (EP/C534212/1) and in part by the EEC Framework 6 Program through the Network of Excellence "DfMM PATENT, Design for Micro and Nano-Manufacture" under Contract Number 507255 as well as the INFOTERM NKFP-2/0018/2001 and the OTKA TS04989 projects of the Hungarian Government. This work was recommended for publication by Associate Editor T. Lee upon evaluation of the reviewers comments.

M. P. Y. Desmulliez, M. Leonard, R. S. Dhariwal, W. Yu, and E. Abraham are with the MIcroSystems Engineering Center (MISEC), School of Engineering and Physical Sciences, Heriot–Watt University, Edinburgh EH14 4AS, U.K. (e-mail: m.desmulliez@hw.ac.uk).

A. J. Pang is with the Institute of Bioengineering and Nanotechnology (IBN), The Nanos, #04-01 Singapore 138669.

Gy. Bognár, A. Poppe, Gy. Horvath, Zs. Kohari, and M. Rencz are with the Department of Electron Devices, Budapest University of Technology and Economics, H-1111 Budapest, Hungary.

D. R. Emerson and R. W. Barber are with the STFC Daresbury Laboratory, Daresbury, Warrington WA4 4AD, U.K..

O. Slattery, F. Waldron, and N. Cordero are with the Tyndall Institute, University College, Cork, Ireland.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCAPT.2008.2002434

scale [4]. More specifically, the research presented here concentrates on single-phase forced-convection heat sinks based on microchannel plates [5] which receive forced-air convection from a 3-D electromagnetic microfan manufactured using microengineering techniques. Details of the fan construction are given in [6].

The concept of microchannel cooling is over 25 years old [7], [8]. The idea of microfabrication of micro cooling channels using an axisymmetric configuration was first reported by Joo, Dieu, and Kim at the IEEE MEMS'95 meeting [9]. In their work, the channels are only 8–10  $\mu$ m high and their width is only 5–10  $\mu$ m. However, the system presented in this paper is a new application of the UV-LIGA process consisting of growing a doubly electroformed layer of nickel for the base and the microchannels, respectively. The channel dimensions are approximately 70  $\mu$ m high and 100  $\mu$ m wide. The emphasis of this work is in presenting a cost-effective solution that can potentially be manufactured directly on the back of a wafer used to grow electronic chips thereby allowing a reduction in the number of interfaces.

In addition, the purpose of this paper is to present a suite of unique thermal characterization techniques that can be applied to various thermal management problems in the microelectronics as well as the MEMS industry. Prior publications on advanced forced-flow cooling solutions (such as [10], for example) dealt mainly with the characterization of the flow. In this paper, a thermal characterization method of cooling assemblies is presented through the example of a nickel-based radial microchannel cooling plate [6]. The devices described in [3] are in the channel diameter range of 250–1000  $\mu$ m, whereas the characteristic width and height of the cooling channel is 100  $\mu$ m and 70  $\mu$ m, respectively. Section II gives a description of the design and manufacturing process performed to create such devices. These cooling elements are modeled in Section III using analytical equations and finite-element analysis (FEA) in order to assess the flow rate as a function of the pressure of the liquid or gas input into the channels. Section IV presents the experimental setup and testing procedures used to measure the flow rate. The thermal characteristics of the micro-cooler are presented in Section V by thermal transient measurements. Conclusions are summarized in Section VI.

#### II. MANUFACTURING OF THE MICROCHANNEL COOLING PLATE

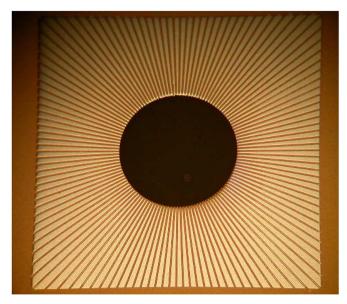

The microchannel cooling plate studied is shown in Fig. 1. The plate supports a total of 128 channels each  $100 \, \mu \text{m}$  wide that radiate from the center outwards. The shortest channel length is 4.5 mm and the longest is 7.61 mm. The side of the square plate

Fig. 1. Top view of the nickel electroformed microchannel cooling plate after lift off from the glass substrate. The plate is composed of 128 radial channels of  $100-\mu m$  width and  $70-\mu m$  depth.

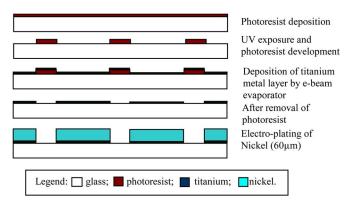

Fig. 2. Fabrication process of the first layer.

is 15 mm in length and its thickness is 130  $\mu$ m as measured from its base to the top of the channels. The support is 60  $\mu$ m thick thus providing 70  $\mu$ m of depth for the channels. A 6-mm diameter hole is located at the center of the plate for the fan to be fitted in. Details regarding the manufacturing of the fan can be obtained in [6]. The whole channel plate is made using a two-layer electroforming UV-LIGA process. Two photo masks, designed with the CAD-software layout edit (L-EDIT) are used for the holes and the channels.

# A. Fabrication of the First Layer

The first layer defines the base of the cooling plate and the position of the center holes. Fig. 2 shows the fabrication process. First a 3-in glass wafer is thoroughly cleaned and then dried in an oven at 60 °C for 20 min. After cooling to room temperature, a positive photoresist AZ 9260 is spin-coated on to the wafer with a spin speed of 2800 rpm for 20 s. A delay of 4 min is allowed for the photoresist to settle down on the wafer before baking. The wafer is then baked in two steps on a hot plate to evaporate the solvent; the first step is at 78 °C for 20 s and then at 103 °C for 330 s. The wafer is then removed from the hot plate

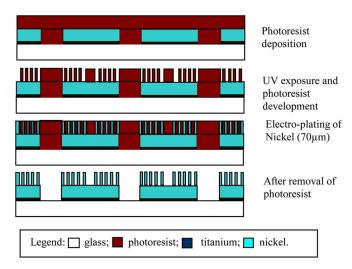

Fig. 3. Fabrication process for the second layer.

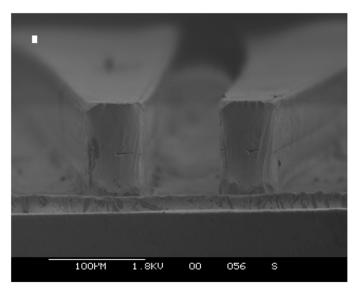

Fig. 4. Cross-sectional image of the microchannel taken by SEM.

and allowed to cool down to room temperature for about 40 min before UV-exposure. An exposure dosage of 800 mJ/cm<sup>2</sup> at the I-line is used to expose the photoresist. After exposure, the wafer is developed using diluted AZ400K developer for 4 min (the ratio of AZ developer to deionized water is 1:3). As a result, a 5–6  $\mu$ m thick layer of photoresist is achieved. A 300-nm thick titanium layer is then deposited onto the photoresist using an electron-beam evaporator. Then a liftoff process is conducted by stripping off the photoresist in EC solvent and thus the center holes for the microchannel cooler are defined where should be no titanium layer. This layer constitutes the seed conductive layer for the subsequent electroplating processes. Nickel is then electroformed on to the titanium seed layer with a low current of 68 mA for 2 h, followed by a higher current of 198 mA for about 14 h. As a result, a  $60-\mu$ m-thick electroplated nickel layer is achieved for the first layer as shown in Fig. 2.

### B. Fabrication of the Second Layer

The second layer defines the microchannels and the fabrication process for the second layer is shown in Fig. 3. After

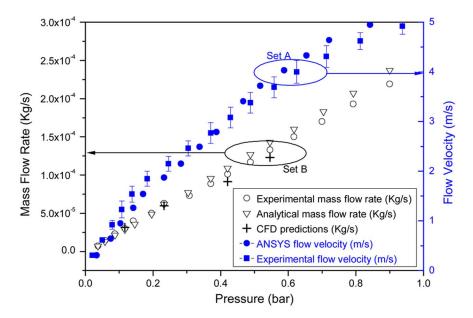

Fig. 5. Graphs of experimental, analytical, and simulation results showing flow velocity (m/s) versus applied pressure (bar) and mass flow rate (kg/s) versus pressure (bar). The mass flow rate is defined as the product of the volumetric flow rate ( $m^3/s$ ) and the density (kg/ $m^3$ ). The volumetric flow rate ( $m^3/s$ ) is calculated by multiplying the mean inlet flow velocity (m/s) of the fluid by the cross-sectional area of the feeding tube.

finishing the electroplating of the first layer, the wafer is then cleaned and dried with deionized water. A 70- $\mu$ m photoresist is then deposited onto the wafer by a two-layer coating process. For each layer, a spin speed of 1000 rpm and spin time of 8 s are used. In between the two-layer coating, a prebaking stage was conducted at 68 °C for 30 s, then at 80 °C for 20 s, and finally at 103 °C for 3 min. After coating the second layer, the same prebaking parameters are applied except that the time at 103 °C is increased to 6 min. After baking, the wafer is removed from the hot plate and allowed to cool down to room temperature for 1 h before exposure. The second mask is aligned with the first pattern with the help of mask alignment marks on the wafer and mask. The wafer is then exposed to UV light with an energy dose of 2200 mJ/cm<sup>2</sup>. After exposure, the wafer is developed in AZ 400 K developer for 12–16 min. Nickel is then electroplated again to obtain a microchannel thickness of 70  $\mu$ m with a current of 68 mA for 2 h followed by a current of 128 mA for 16 h. The photoresist is then stripped off using an organic solvent in an ultrasonic bath to obtain the desired microchannels. Finally, the electroplated nickel microchannel device structure is lifted off resulting in the successful fabrication of the cooling plate as shown in Fig. 1 (SEM pictures of the micro-cooler channels near to the middle hole can be seen in Fig. 4). The walls and the bottom side of the channels are sufficiently smooth so as not to disturb the gas flow through the channels.

# III. DETERMINATION OF THE FLOW RATE THROUGH THE MICRO-COOLER

#### A. Incompressible Analytical Solution

The volumetric flow rate Q (m<sup>3</sup>/s) for isothermal, fully developed, incompressible, laminar flow through a rectangular duct

can be expressed as a function of the pressure gradient dp/dx (Pa/m) as follows [11]:

$$Q = \frac{4ba^3}{3\mu} \left( -\frac{dp}{dx} \right) \left[ 1 - \frac{192a}{\pi^5 b} \sum_{i=1,3,5,\dots}^{\infty} \frac{\tanh(i\pi b/2a)}{i^5} \right]$$

(1)

where  $\mu$  is the dynamic viscosity of the fluid (Ns/m²) and 2a and 2b are the width and height of the channel, respectively. The present micro-cooler has a total of 128 radial channels but by taking advantage of symmetry, only 15 full channels and two half-channels (i.e., one-eighth of the total number) need to be considered when determining the flow rate through the device. With a fixed pressure applied to the central inlet aperture, the pressure gradient  $\mathrm{d}p/\mathrm{d}x$  in each of the channels will be different due to the varying channel lengths. The total volumetric flow rate can thus be estimated by summing the contribution from each of the individual pressure gradients. Once the total volumetric flow rate is known, it can readily be converted into a mass flow rate by multiplying by the density of the fluid.

#### B. Computer Simulations

Computational fluid dynamics (CFD) simulations have been used to provide a better estimate of the flow rate through the micro-cooler. The aim of the CFD simulations was to provide an understanding of the mass transport through the device rather than a detailed thermal characterization. The numerical simulations employed the finite-element analysis (FEA) software package from ANSYS, Inc., and the commercial computational fluid dynamics solver, CFD-ACE+ from ESI-CFD [12]. To reduce the computational cost of the simulations, only one-eighth of the micro-cooler was considered and symmetry boundary

Fig. 6. Schematic diagram (top) and picture (bottom) of the experimental setup.

conditions were applied along the center line of the shortest (4.5 mm) and longest (7.61 mm) channels.

When considering the flow conditions in noncircular ducts, the Reynolds number is usually defined using the *hydraulic diameter*  $D_{\rm h}$  as the characteristic length scale [11], i.e.,

$$D_{\rm h} = \frac{4 \times \text{area}}{\text{wetted perimeter}}.$$

(2)

The Reynolds number can then be defined as follows:

$$Re = \frac{\rho v_{\rm av} D_{\rm h}}{\mu} \tag{3}$$

where  $\rho$  is the fluid density (kg/m<sup>3</sup>) and  $v_{\rm av}$  is the average velocity through the duct (m/s). In the present study, the Reynolds number was found to vary between approximately 50 and 1500,

implying the flow within the micro-cooler is laminar. In addition, the Knudsen number at the outlet, defined as

$$Kn = \frac{\lambda}{D_h} \tag{4}$$

where  $\lambda$  is the mean free path of the gas molecules, was found to be less than  $10^{-3}$ , implying that the no-slip/no-temperature-jump boundary conditions used in conventional (continuum) fluid mechanics are valid [13]. The simulations using CFD-ACE+ were performed by varying the overall pressure difference across the device by systematically changing the inlet pressure while keeping the outlet pressure fixed at atmospheric. In contrast, the simulations using ANSYS were performed by specifying a fixed atmospheric pressure at the downstream boundary and varying the mean flow velocity across the inlet aperture. In both cases, isothermal boundary conditions were implemented along the channel walls.

The simulations using CFD-ACE+ employed a grid composed of  $16 \times 16$  cells for the channel cross section and 100 cells along the length of each channel giving a total of approximately 440 000 cells for the one-eighth symmetry domain  $(\sim 3.5 \text{ million cells for the entire micro-cooler})$ . This was sufficient to gather reliable flow data and was a compromise between accuracy and time to solution. The choice of grid size was based on extensive experience gained from previous validation studies on a range of two- and three-dimensional laminar flows. Similarly, the ANSYS simulations employed  $6 \times 8$  cells for the channel cross section and 128 cells along the length of each channel. Both sets of CFD simulations accounted for a number of important factors that cannot be modeled using the incompressible, fully developed, analytical solution shown in (1). For example, the numerical simulations were able to account for density/temperature variations and were able to model the pressure losses at the entrance to the channels.

Two sets of flow results are presented in Fig. 5. Set A shows the experimental and simulated (ANSYS) results for the flow velocity at the inlet aperture versus the applied pressure. It can be seen that both the experimental and simulated results show a nonlinear trend of inlet velocity against applied pressure—a common feature of compressible flows. However, by recasting the data in terms of the mass flow rate (Set B), the experimental and simulated results then show an almost linear variation of mass flow rate against applied pressure. Set B shows that the incompressible analytical solution is in very good agreement with the experimental data up to a pressure of approximately 0.25 bar. Thereafter, the deviation becomes larger due to the fact that the analytical solution fails to account for hydrodynamic losses at the entrance of the microchannels. In addition, the incompressible flow assumption embedded in (1) starts to break down at higher pressure ratios. It can be seen that the results presented in Fig. 5 (Set B) suggest that the chosen grid resolution for the CFD predictions is sufficient because the analytical solution and the CFD solution are in excellent agreement at the lower flow rates when compressibility effects and entrance losses are minimal. One might note that data Set A for flow velocity has a larger deviation between simulated and experimental results than that of data Set B. The reasons for this de-

Fig. 7. Microchannel plate attached to a power transistor (BD245C) with the heat-flow sensor placed in between them.

viation are twofold. First, the cross section of the microchannel is nonrectangular and this is not taken into account in the simulation. More importantly, when recasting the flow velocity in terms of the mass flow rate, a varying density of the gas at different pressure and therefore different flow velocity was used. The resulting curve of data Set B for mass flow rate shows a more linear trend and a relatively little deviation between experimental and simulation results.

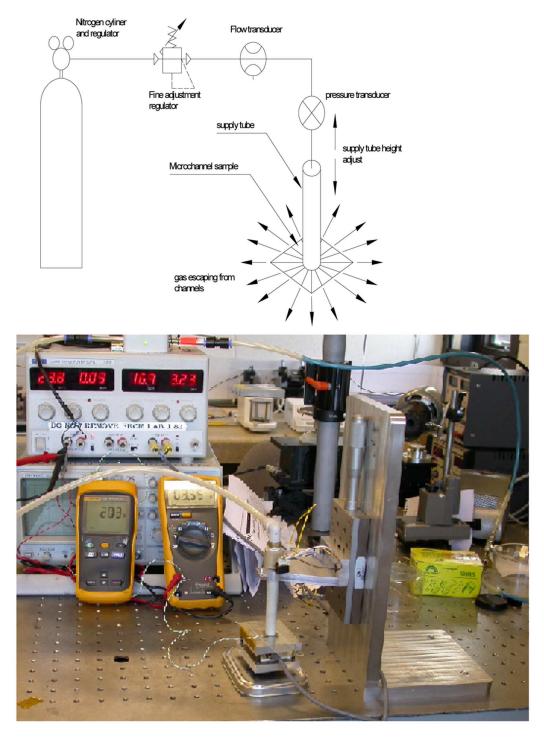

#### IV. MEASUREMENT OF THE MICRO-COOLER FLOW RATE

Fig. 6 shows the experimental setup used in the measurement of the pressure drop in the microchannels. The pneumatic system supplying nitrogen to the test sample consists of a standard oxygen-free nitrogen supply with regulator, a second regulator for fine pressure control, a gas flow meter, pressure gauge, and purpose-built fitting to supply the gas to the sample aperture. The fine adjustment regulator is a Parker PD3 diaphragm type; the flow transducer is a Weber type 3202 meter and the pressure gauge is a Sandhurst LH44. All components are connected in series using 5-mm ID flexible plastic tubing. The design of the supply tube allows the gas to be supplied at one end and the opposite end mates with the central aperture and seals with a fitted rubber "O" ring. The tube is mounted vertically and attached to a micrometer translator, which allows the tube end to be held firmly against the sample without leaking.

The microchannel sample was mounted on a firm glass substrate base, with the channels facing towards the substrate; this effectively closes the channels and allows the gas to flow from the central cavity, through the channels and out into free space. Gas flow was then initiated and the pressure adjusted to produce the maximum gas flow to give a full-scale reading on the flow meter which has a resolution of 0.01 m/s. A flow of 5 m/s corresponds to a 20-mA reading from the output circuit. A pressure reading is then taken. The regulator is then adjusted to reduce the flow by a small amount and new pressure and flow rate readings are taken. This process was then repeated many times until the readings reached a zero flow measurement. A graph of pressure against flow rate was then plotted. Several identical tests were conducted on the same sample to check for repeatability. An additional test was conducted to check the flow from the device and establish that all channels were operating and that there were no leaks at the device inlet. This was done by submerging

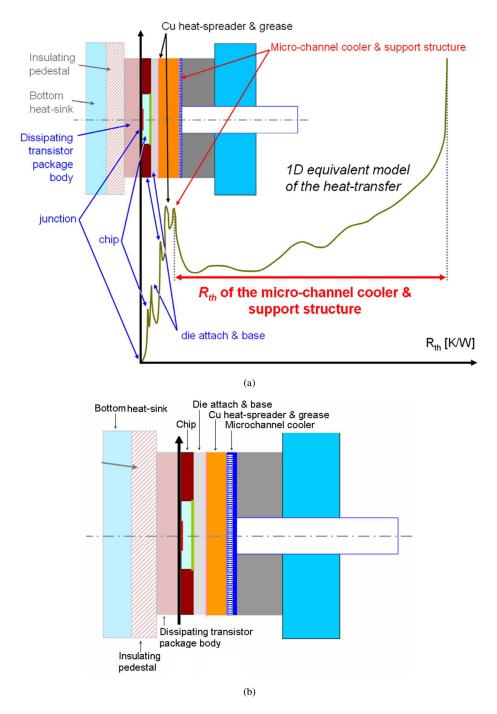

Fig 8. (a) Differential structure function of the power transistor, micro-cooler, and its support setup. (b) Details of the experiment setup in (a).

the entire microchannel device in a few centimeters of water to allow a visual check for bubbles from all channel ends.

#### V. DEVICE THERMAL TRANSIENT MEASUREMENT

## A. Measurement Setup and Procedure

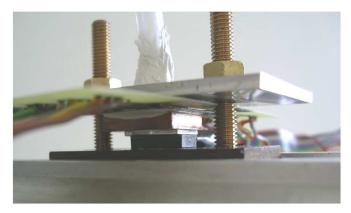

The efficiency of the microchannel cooler can be characterized either by its thermal resistance or its heat-transfer coefficient. In order to measure the thermal resistance, the microcooling plate is attached to a heat-dissipating element, in this

case a BD245C power transistor, as shown in Fig. 7. A flat surface copper plate of  $15 \times 15 \times 2 \text{ mm}^3$  is used as a heat spreader. The micro-cooler is mounted so that the channels were facing the flat copper plate or the heat-flow sensor. The gas supply tube, seamlessly joined to a silicone rubber sheet ensured the cooling gas flows to the central (fan) hole. The rubber sheet protected the micro-cooler plate from breaking. Both the powering of the transistor and sensing its temperature change was carried out using a T3Ster thermal transient tester. The heat-flow map provided by the sensor array was recorded during the measurements.

<sup>1</sup>[Online]. Available: www.micred.com/t3ster.html.

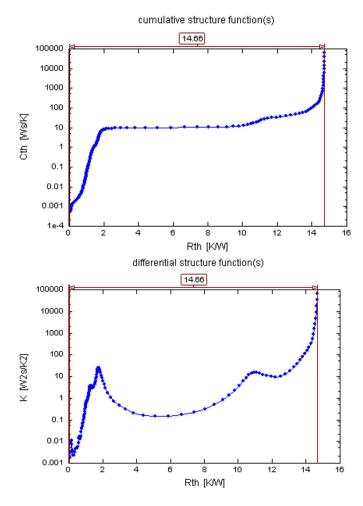

Fig. 9. (a) (top) and (b) (bottom). Identification of the thermal resistances of the micro-cooler and its support structure at a flow-rate of 120 l/h.

Measurement of the operating transistor temperature rise together with knowledge of the applied electrical power step and temperature rise of the junction  $\Delta T_j$  are used for the calculation of the junction-to-ambient thermal resistance

$$R_{\rm thja} = \frac{\Delta T_j}{\Delta P}.$$

(5)

By repeating this measurement at different flow rates of the coolant gas, the variation of the thermal resistance as a function of the flow rate can be obtained. The junction temperature rise of the transistor can be identified by the principles of the electrical test method [14]. The forward voltage of the emitter—base junction is a temperature-sensitive parameter whose sensitivity is determined in a calibration process by letting a small sensor current (e.g., 1 mA) flow across the junction. The value of  $\Delta T_j$  must be measured from steady-state to steady-state. The thermal resistance identified in this fashion includes unwanted thermal resistances of the transistor, copper heat-spreader and microcooling plate.

The calculation of thermal resistance of the micro-cooler and its support assembly can be obtained by using structure functions determined through thermal transient measurements [15],

Fig. 10. Change of thermal resistance with respect to the flow-rate through the micro-cooler.

[16]. The continuous measurement of the temperature contains all available information about the junction-to-ambient heat conduction path, starting from the transistor junction up to the micro-cooling plate and its support assembly. In our setup most of the dissipated power is directed towards the micro-cooler as the power transistor is placed on to an insulating pedestal. In order to cross-verify the measured results, a heat-flow sensor array is also inserted between the micro-cooler and the copper heat-spreader as shown in Fig. 7. The heat-flow sensor array introduces only a negligible serial thermal resistance. The parasitic heat-flow across the insulating pedestal is negligible, but can also be measured during the structure-function-based evaluation as described in [18]. The concept of extracting information from the high resolution, noise-free thermal transients is well documented in a number of publications [14]-[18] and will not be reproduced here.

Fig. 8(a) represents the differential structure function of the power transistor/microchannel cooler setup of Fig. 7 when no gas flows through the cooler. Fig. 8(b) shows the details of the experiment setup. The origin of the curve always corresponds to the junction and the function always ends with a singularity indicating the infinite thermal capacitance of the ambient. Peaks in the differential structure functions indicate transitions between material regions which constitute interfaces of the major elements of the setup heat-flow path. Even structural elements inside the transistor package can be identified. The last peak is interesting, since it shows the thermal interface between the copper heat-spreader and the micro-cooler with its support assembly. While the singularity shows the thermal interface between the micro-cooler and the ambient. Thus the distance between the last peak location and the singularity gives the thermal resistance between the micro-cooler and the support structure. A resulting lumped element model of the device under test can subsequently be extracted from the structure function.

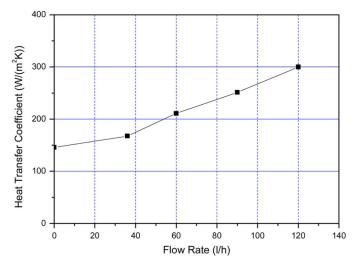

Fig. 11. Effective heat transfer coefficient with respect to the flow rate.

#### B. Measurement Results

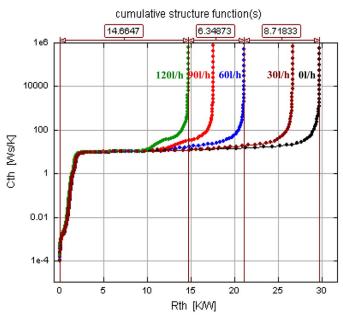

In order to measure the thermal characteristics of the micro-cooler, the transistor is first heated up and allowed to reach a steady state. The power step applied to the transistor is 3.5 W. The cooling gas flow is then started and the cooling transients at different flow rates are recorded. The thermal transient responses are measured at different gas flow rates (from 0 l/h to 120 l/h). The ambient air temperature of the laboratory is 23.5 °C and the air pressure is 1.006 bar. Each measured thermal transient is evaluated and the corresponding structure functions generated. The boundaries between the different regions of the heat-flow path are well pronounced as peaks in the differential structure function shown in Fig. 9(a). The thermal resistance between the copper heat-spreader/micro-cooler interface and the ambient can be identified in this way. The thermal characteristics of the micro-cooler and its support assembly  $(R_{\rm th}, C_{\rm th})$  thermal resistance and capacitance values, respectively) are better read from the cumulative structure functions as shown in Fig. 9(b). The change of the thermal resistance with respect to the change of flow rate is identified from the cumulative structure function, as shown in Fig. 10.

The measured thermal resistance is presented in Fig. 10 as a function of the flow rate. This part of the thermal resistance corresponds to the heat transfer due to the gas flow in the microchannels only. With a small change in the flow rate, smooth changes occur in the lumped thermal resistance value of the cooler setup. At 120 l/h however, the shape of the structure function significantly differs from the other functions (see Fig. 10). This suggests that, around these flow rate values, some characteristic changes take place in the gas-flow. It can also be seen from Fig. 10 that the larger the flow rate, the smaller the thermal resistance. The differential structure function reflects the thermal resistance distribution in the heat flow path. As can be seen, the thermal resistance of the micro-cooler is the largest, with a value of around 12.5 K/W while for the other components, the thermal resistance is very small and the sum of the resistance for all of these components (including the copper heat spreader and the transistor) is only 2 K/W.

Once the thermal resistance of the micro-cooler is obtained, the effective heat transfer coefficient of the micro-cooler can be calculated by the following formula [19]

$$\lambda = 1/(rA) \tag{6}$$

where  $\lambda$ , r, and A is the heat coefficient, thermal resistance, and cross section area of heat-conduction path of the microchannel cooling plate. By applying the above formula, the effective heat transfer coefficient of the micro-cooler was calculated as 300 W/m² K at a flow rate of 120 l/h. The values of the effective heat transfer coefficient of the micro-cooler at different flow rates have been calculated by above formula and are shown in Fig. 11.

#### VI. CONCLUSION

A novel method of fabricating microchannel cooling plates using a cost-effective UV-LIGA process has been demonstrated. Testing of the flow rate of the device has been successfully carried out using an in-house test rig. The measurements of the flow rate agree very well with the modeling and simulation results of the whole device carried out by analytical and FEA methods. With the help of structure functions, the thermal resistances of the test setup, and the micro-cooler plate itself were measured. The thermal characteristics (resistance and capacitance) of the device at different flow rates were also obtained. The sudden change observed in the shape of the structure functions suggests that at a certain flow rate, the nature of the flow inside the microchannel cooler changes. The heat-transfer coefficient versus flow rate functions has been obtained by the structure functions.

#### REFERENCES

- SEMATECH, International Technology Roadmap for Semiconductors—Assembly and Packaging, ITRS 2005 Update, 2005.

- [2] I. Sauciuc, G. Chrysler, R. Mahajan, and M. Szleper, "Air-cooling extension—Performance limits for processor cooling applications," in *Proc. 20th SEMI-THERM Symp.*, San Jose, CA, Mar. 11–13, 2003, pp. 74–80.

- [3] S. V. Garimella, "Advances in mesoscale thermal management technologies for microelectronics," in *Proc. 10th THERMINIC Workshop*, Sophia-Antipolis, France, 29 Sep.–Oct. 2004, pp. 185–206.

- [4] P. Rogers and V. Eveloy, in Proc. IEEE 5th Int. Conf. Thermal and Mechanical Simulation and Experiments in Micro-Electronics and Micro-Systems, EuroSim E, 2004, pp. 527–529.

- [5] R. Hahan, A. Kamp, A. Ginolas, M. Schmidt, J. Wolf, V. Glaw, M. Toepper, O. Ehrmann, and H. Reichl, "High power multichip modules employing the planar embedding technique and microchannel water heat sinks," *IEEE Trans. Compon., Packag., Manuf. Technol.*, vol. 20, no. 4, pt. A, pp. 432–441, Dec. 1997.

- [6] A. J. Pang, M. P. Y. Desmulliez, M. Leonard, R. S. Dhariwal, R. L. Reuben, A. S. Holmes, G. Hong, K. R. Pullen, F. Waldron, O. Slattery, M. Rencz, D. R. Emerson, and R. W. Barber, "Design, manufacture and testing of a low-cost microchannel cooling device," in *IEEE Proc. 6th Electron. Packag, Technol. Conf.*, Singapore, Dec. 8–10, 2004, pp. 564–568, ISBN 0-7803-8821-6.

- [7] L. Zhang, K. E. Goodson, and T. W. Kenny, Silicon Microchannel Heat Sinks. New York: Springer-Verlag, 2004.

- [8] D. B. Tuckerman and R. F. Pease, "High-performance heat sinking for VLSI," *IEEE Electron. Device Lett.*, vol. EDL-2, no. 5, pp. 126–129, Sep. 1981.

- [9] Y. Joo, K. Dieu, and C.-J. Kim, "Fabrication of monolithic microchannels for IC chip cooling," in *Proc. IEEE Micro Electro Mechanical Systems (MEMS'95)*, Jan 29–Feb 2 1995, pp. 362–367.

- [10] C. Li and R. A. Wirtz, "Development of a high performance heat sink based on screen-fin technology," in *Proc. 20th SEMI-THERM Symp.*, San Jose, CA, Mar. 11–13, 2003, pp. 53–60.

- [11] F. M, White, Fluid Mechanics. New York: McGraw-Hill, 1991.

- [12] "CFD-ACE+ User Manual (2006) ESI CFD," Huntsville, AL, 2006.

- [13] R. W. Barber and D. R. Emerson, "Challenges in modeling gas-phase flow in microchannels: From slip to transition," *Heat Transf. Eng.*, vol. 27, no. 4, pp. 3–12, 2006.

[14] B. S. Siegal, "Measuring thermal resistance is the key to a cool semi-

- [14] B. S. Siegal, "Measuring thermal resistance is the key to a cool semi-conductor," *Electronics*, vol. 51, pp. 121–126, 1978.

[15] Székely, "Tran van bien, Fine structure of heat flow path in semicon-

- [15] Székely, "Tran van bien, Fine structure of heat flow path in semiconductor devices: A measurement and identification method," *Solid-State Electron.*, vol. 31, no. 9, pp. 1363–1368, 1988.

- [16] V. Székely *et al.*, "New way of thermal transient testing," in *Proc. 15th SEMI-THERM Symp.*, San Diego, CA, Mar. 9–11, 1999, pp. 182–188.

- [17] M. Rencz et al., "Determining partial thermal resistances with transient measurements and using the method to detect die attach discontinuities," in *Proc. 18th SEMI-THERM Symp.*, San Jose, CA, Mar. 10–14, 2002, pp. 15–20.

- [18] M. Rencz, A. Poppe, E. Kollár, S. Ress, V. Székely, and B. Courtois, "A procedure to correct the error in the structure function based thermal measuring methods," in *Proc. 20th SEMI-THERM Symp.*, San Jose, CA, Mar. 9–11, 2004, pp. 92–98.

- [19] V. Székely, "A new evaluation method of thermal transient measurement results," *Microelectron. J.*, vol. 28, pp. 277–292, 1997.

M. P. Y. Desmulliez (M'08) was born in Lille, France, in 1963. He received the French diploma of electrical engineering from the Ecole Superieure d'Electricite of Paris (Supelec) in 1987, two college diplomas from University College London and the University of Cambridge and the Ph.D. degree in optoelectronics from Heriot-Watt University, Edinburg, U.K., in 1995.

He is the Director of the MIcroSystems Engineering Center (MISEC), an organization that regroups the expertise in MEMS of six academic

members of staff and 30 Ph.D. students and research associates. His research interests are in MEMS design and manufacturing for applications ranging for health, microelectronics packaging, and electronic systems monitoring.

Dr. Desmulliez is a member of the IET, IMAPS-UK and the Institute of Physics.

A. J. Pang, photograph and biography not available at the time of publication.

M. Leonard was born in England in 1960. He received the Honours degree in metallurgy and materials engineering in London by part-time study while working for the 3M Company at their Imaging and Data storage research facility in Essex, U.K.

He has worked on a wide range of research projects from building novel chemical processing systems to experimental film processors and solid-state optically stimulated thermal imaging systems. He is currently overseeing the cleanroom at the MIcroSystems Engineering Center (MISEC), School of

Engineering and Physical Sciences, Heriot-Watt University, Edinburgh, U.K., and associated MEMS fabrication equipment and is involved with teaching.

R. S. Dhariwal joined the Electrical and Electronic Engineering Department, Heriot-Watt University, Edinburgh, U.K., in 1978 and was promoted to Senior Lecturer in 2003. The name of the department was changed to Electrical, Electronic, and Computer Engineering and it is now within the School of Engineering and Physical Sciences. He is Course Director of the M.Sc. in Microsystems Engineering at Heriot-Watt and this course was in receipt of substantial funding from the EPSRC. The course has been revised and is now known as the M.Sc. in

Microsystems with Photonics. He was the Principal Investigator of the EPSRC grant "Microengineered axial-flow pumps and turbines" (GR/N18925), the results from which form the basis of the work presented in this paper.

W. Yu received the B.Sc. degree from Northwestern Polytechnical University, Xi'an, China, in 1998, the M.Sc. degree from Changchun Institute of Optics, Fine Mechanics, and Physics, Changchun, China, in 2001, and the Ph.D. degree from Nanyang Technological University, Singapore, in 2005.

He is now with the MIcroSystems Engineering Center (MISEC), School of Engineering and Physical Sciences, Heriot-Watt University, Edinburgh, U.K., as a Postdoctoral Research Associate. His research interests are in microfabrication, microoptics,

and microelectronics packaging.

**E. Abraham** was born in Israel in 1951 and grew up in Argentina. He received the B.Sc. degree from the University of Buenos Aires, Buenos Aires, Argentina, in 1975 and the Ph.D. degree from the University of Manchester, manchester, U.K., in 1979.

After postdoctoral work, he became a Lecturer at Heriot-Watt University, Edinburgh, U.K., in 1983 and a Senior Lecturer in 1996. His initial research interests were in theoretical quantum and nonlinear optics. His interest moved to Josephson junction circuits. His present research interests are high-temperature super-

conductivity, magnetoelectricity and engineering the vacuum energy. Being the cofounder of a high-technology company in the area of microelectronics packaging motivated him to get involved in related engineering problems. He has worked as a Visiting Scientist in European countries, the former USSR, and the U.S. He is also a Non-Executive Director of MicroStencil, Ltd.

**Gy. Bognár** received the Ms.C. degree in electronic engineering from the Faculty of Electrical Engineering and Computer Science, Budapest University of Technology and Economy, Budapest, Hungary, specialization in microelectronics, and cable television systems. From 2002 to 2005, he was a Ph.D. student at the Department of Electron Devices.

Since 2007, he has been a Senior Lecturer in the Department of Electron Devices, Budapest University of Technology and Economy. His research fields are noncontact thermometry, thermal charac-

terization of microchannel structures and different MEMS elements, CAD of integrated circuits, design of mixed-signal integrated circuits, and investigating parasitic effects of IC packaging.

**A. Poppe** (M'99) received the M.Sc. degree in electrical engineering and the Ph.D. degree from the Faculty of Electrical Engineering, Technical University of Budapest (BME), Budapest, Hungary, in 1986 and 1996, respectively.

His first research field was circuit simulation and semiconductor device modeling. From 1989 to 1990, he spent a year at IMEC, Leuven, Belgium, where he was dealing with mobility modeling for the purpose of 2-D device simulation. Since 1990, he has been with BME. He participated in the development of cir-

cuit and device simulation programs. From 1991 to 1994, he was active in the field of Monte Carlo simulation of submicrometer MOS devices. Currently, he is an Associate Professor at BME. His recent research activities electrothermal simulation of integrated circuits as well as thermal transient testing of semiconductor devices and combined thermal and radiometric measurement of power LEDs. He was actively involved in European projects such as PROFIT, SYTIC, REASON, and in national R&D projects like INFOTERM or TERALED. He has also been principal investigator in some of these projects. He is one of the cofounders of MicReD. His responsibilities at MicReD include product management of thermal transient testing solutions. Currently, he is the representative of MicReD in the NANOPACK Integrated Project of the 7th Framework Program of the EU. As an author and coauthor, he has published more than 200 technical papers in journals and in conference/workshop proceedings.

**Gy. Horvath,** received the M.Sc. degree in electronic engineering from the Faculty of Electrical Engineering and Computer Science, Budapest University of Technology and Economy, specializing in microelectronics, and cable television systems. From 2004 to 2007, he was pursuing the Ph.D. degree at the Budapest University of Technology and Economy.

Since 2005, he has been an Assistant Lecturer in the Department of Electron Devices, Technical University of Budapest (BME). His research fields are in

design of analog and digital VLSI circuits and MEMS structures, thermal characterization of MEMS structures, laser interferometry, nanometric-scale dilatation measurements, and battery modeling. His other interests are ambient intelligence, developing electronic systems, computer technology, embedded system design, thermal characterization and modeling, and robotics.

**Zs. Kohari,** received the M.Sc. degree in electrical engineering from the Faculty of Electrical Engineering, Budapest University of Technology and Economy, in 1991.

He has been with the Department of Electron Devices, Technical University of Budapest (BME) since 1991. His field of interest includes the different aspects of the thermal behavior of integrated circuits, microstructures, and packages. He participated in different national and European projects.

M. Rencz (M'96) received the electrical engineering degree in 1973 and the Ph.D. degree in 1980, both from the Technical University of Budapest, Budapest, Hungary.

Her first research area was the simulation of semiconductor devices. Later, she participated in the development of several CAD programs in microelectronics. Her latest research interests include the thermal investigation of ICs and MEMS, thermal sensors, thermal testing, thermal simulation, and electrothermal simulation. She is cofounder and

CEO of MicRed. She has published her theoretical and practical results in more than 300 technical papers.

Dr. Rencz is a member of IMAPS. She is an organizing committee and program committee member of several international conferences and workshops. For her research results in thermal modeling, she has received the Harvey Rosten Award of Excellence from the electronics thermal management community.

**D. R. Emerson,** photograph and biography not available at the time of publication.

R. W. Barber, photograph and biography not available at the time of publication.

**O. Slattery** received the B.E. degree in civil engineering, the M.Eng.Sc. degree in civil engineering, and the M.Eng.Sc. in electronics, all from University College Cork, Cork, Ireland, in 1989, 1991, and 1998, respectively.

In 1991, she joined the Interconnection and Packaging Group, NMRC, Cork, where she was responsible for simulation and characterization of thermal and thermomechanical issues in electronics components and systems. Since 1999, she has been working as a Research Scientist with the Computational Mod-

eling Group, NMRC, She has participated in a number of European Union- and Irish Government-funded projects as well as providing services to Irish and European Industry. Her current research interests include the application of computational simulation tools to the solution of thermal and thermomechanical problems in microelectronics components and systems. She has published a range of papers in these areas. She is also involved in modeling and simulation of MEMS and is currently Vice-Chair of the EU-funded Network of Excellence on Design for Micro and Nano manufacture, PATENT-DfMM.

**F. Waldron,** photograph and biography not available at the time of publication.

N. Cordero, photograph and biography not available at the time of publication.